「同期/非同期リセットでの生成回路の違い(1)」の合成結果でつぎのようにでていました。

| ケース0 | ケース1 | ケース2 | ケース3 | ケース4 | |

|---|---|---|---|---|---|

| 同期/非同期 | なし | 非同期 | 同期 | 同期 | 非同期 |

| LUT | 2 | 3 | 3 | 3 | 3 |

| FF | 1 | 1 | 2 | 1 | 2 |

| IO | 9 | 10 | 10 | 10 | 10 |

| BUFG | 1 | 1 | 1 | 1 | 1 |

ケース3は同期リセット、ケース4は非同期リセットを想定して記述したものでしたが上記の結果からもケース3にはリセットのFFはなく、ケース4は明示的にFFを置いているのでリセットのFFが存在します。

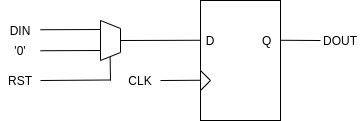

ケース3は次のように構成されてほしかったのです。

ケース3の場合、記述は同期リセットのつもりなのに非同期リセットなのでRecovery TimeとRemoval Timeを考慮する必要があります。

同期リセットで表現したつもりが合成するとRecovery TimeとRemoval Timeが考慮され、動作周波数が低い合成結果か、または、できないかが発生するかもしれません。

ケース4は同期リセットのつもりだけど記述が非同期リセットっぽくなっているが同期リセットで合成されたのはある意味、棚から牡丹餅なのかもしれません。

太古の昔の言い伝えは今、どうなっているか確認するつもりでしたがもう言い伝えは今の時代には通用しなく、新しい問題が発生しているということがわかりました。

XilinxのツールはRSTの名称がついているとリセット信号として通常の信号とは違う扱いにするようです。

ただ、配置配線もリセットにFFがあるので同期リセットっぽい、FFが無いので非同期リセットっぽいのはCellの設定を見ても判断を付けにくい。

ただ、これらの状況から言えるのはケース2やケース4のようにリセットはFFで叩いてから使うのが良いだろう。

そして、ツールを信用するしかない・・・

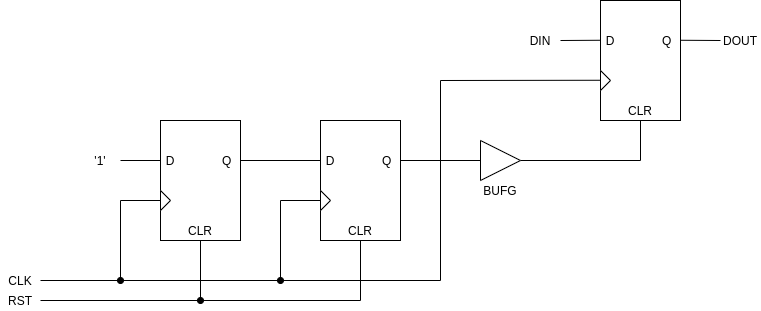

BUFGが余っているなら次のようにRSTを2段FFでメタス回避してBUFGを使用して各FFをリセットするのが良いだろう。